# TriFlash with MultiMediaCard Interface

# **Product Manual**

Revision 1.2 3/2003

# SanDisk Corporation

Corporate Headquarters • 140 Caspian Court • Sunnyvale, CA 94089 Phone (408) 542-0500 • Fax (408) 542-0503

www.sandisk.com

SanDisk® Corporation general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury. Per SanDisk Terms and Conditions of Sale, the user of SanDisk products in life support applications assumes all risk of such use and indemnifies SanDisk against all damages.

The information in this manual is subject to change without notice.

SanDisk Corporation shall not be liable for technical or editorial errors or omissions contained herein; nor for incidental or consequential damages resulting from the furnishing, performance, or use of this material.

All parts of the TriFlash documentation are protected by copyright law and all rights are reserved. This documentation may not, in whole or in part, be copied, photocopied, reproduced, translated, or reduced to any electronic medium or machine readable form without prior consent, in writing, from SanDisk Corporation.

SanDisk and the SanDisk logo are registered trademarks of SanDisk Corporation.

Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

© 2002/2003 SanDisk Corporation. All rights reserved.

SanDisk products are covered or licensed under one or more of the following U.S. Patent Nos. 5,070,032; 5,095,344; 5,168,465; 5,172,338; 5,198,380; 5,200,959; 5,268,318; 5,268,870; 5,272,669; 5,418,752; 5,602,987. Other U.S. and foreign patents awarded and pending.

Lit. No. 80-36-00180 Rev 1.2 3/2003 Printed in U.S.A.

#### Revision History

- Revision 0.1—preliminary draft.

- Revision 0.5—first edits from marketing and engineering.

- Revision 0.6—several minor edits throughout document.

- Revision 0.9—addition of MLC and minor edits throughout document.

- Revision 1.0—removed Stream Read and Stream Write and minor edits throughout document.

- Revision 1.1— Changed power requirements in Section 2.2, Table 2.2; updated addresses in Appendix A

- Revision 1.2— Changed entry in Table 3-1 from "pull up to VDD" to "pull down to VSS".

# Table of Contents

| 1. Introduction to the TriFlash                           | 1-1 |

|-----------------------------------------------------------|-----|

| 1.1. Scope                                                |     |

| 1.2. Product Models                                       | 1-2 |

| 1.3. System Features                                      | 1-2 |

| 1.4. TriFlash with MultiMediaCard Interface Bus Standards |     |

| 1.5. Functional Description                               | 1-3 |

| 1.5.1. Flash Technology Independence                      | 1-3 |

| 1.5.2. Defect and Error Management                        | 1-3 |

| 1.5.3. Endurance                                          | 1-4 |

| 1.5.4. Automatic Sleep Mode                               |     |

| 1.5.5. TriFlash MultiMediaCard Mode                       |     |

| 1.5.5.1. MultiMediaCard Standard Compliance               |     |

| 1.5.5.2. Negotiating Operation Conditions                 | 1-4 |

| 1.5.5.3. Device Acquisition and Identification            |     |

| 1.5.5.4. Device Status                                    |     |

| 1.5.5.5. Memory Array Partitioning                        |     |

| 1.5.5.6. Read and Write Operations                        |     |

| 1.5.5.7. Data Protection in the TriFlash                  |     |

| 1.5.5.8. Erase                                            |     |

| 1.5.5.9. Write Protection                                 |     |

| 1.5.5.10. Copy Bit                                        |     |

| 1.5.5.11. The CSD Register                                |     |

| 1.5.6. TriFlash—SPI Mode                                  |     |

| 1.5.6.1. Negotiating Operating Conditions                 |     |

| 1.5.6.2. Device Acquisition and Identification            |     |

| 1.5.6.3. Device Status                                    |     |

| 1.5.6.4. Memory Array Partitioning                        |     |

| 1.5.6.5. Read and Write Operations                        |     |

| 1.5.6.6. Data Transfer Rate                               |     |

| 1.5.6.7. Data Protection in the TriFlash                  |     |

| 1.5.6.8. Erase                                            |     |

| 1.5.6.9. Write Protection                                 | 1-9 |

|                                                           |     |

| 2. Product Specifications                                 |     |

| 2.1. System Environmental Specifications                  |     |

| 2.2. Typical Power Requirements                           |     |

| 2.3. System Performance                                   |     |

| 2.4. System Reliability and Maintenance                   |     |

| 2.5. Physical Specifications                              |     |

| 3. TriFlash Interface Description                         | 3_1 |

| 3.1. General Description of Pins and Registers            |     |

| 3.1.1. Pin Assignments in MultiMediaCard Mode             |     |

| 3.1.2. Pin Assignments in SPI Mode.                       |     |

|                                                           |     |

| 3.1.3. Registers                                          |     |

| 3.2. MultiMediaCard Bus Topology                          |     |

| 3.3. SPI Bus Topology                                     |     |

| 3.4. Electrical Interface                                 |     |

| 3.4.1. Power-up                                           |     |

| 3.4.2. Bus Operating Conditions                           |     |

| 3.4.3. Bus Signal Levels                                  | 3-7 |

|                                                  | 3-8  |

|--------------------------------------------------|------|

| 3.4.5. TriFlash-Specific Functions               | 3-9  |

| 3.4.5.1. Ready/Busy Function [Output]            | 3-9  |

| 3.4.5.2. Write Protect Function [Input + Pullup] |      |

| 3.4.5.3. Reset Function [Input + Pullup]         |      |

| 3.5. TriFlash Registers                          |      |

| 3.5.1. Operating Conditions Register (OCR)       |      |

| 3.5.2. Card Identification (CID) Register        |      |

| 3.5.3. Card Specific Data (CSD) Register         | 3-12 |

| 3.5.4. Status Register                           | 3-18 |

| 3.5.5. Relative Card Address (RCA) Register      | 3-20 |

| 3.5.6. TriFlash Registers in SPI Mode            | 3-20 |

| 3.6. File System Format                          | 3-20 |

| 4. MultiMediaCard Protocol Description           | 4-1  |

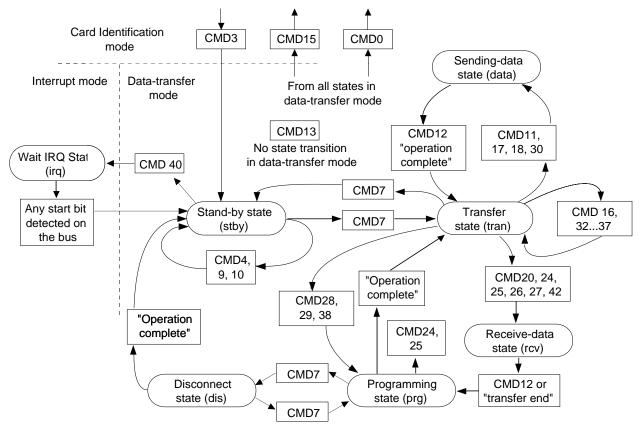

| 4.1. Device Identification Mode                  | 4-2  |

| 4.1.1. Reset                                     | 4-2  |

| 4.1.2. Operating Voltage Range Validation        | 4-3  |

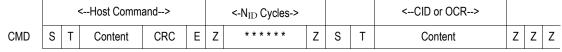

| 4.1.3. Device Identification Process             | 4-3  |

| 4.2. Data Transfer Mode                          | 4-3  |

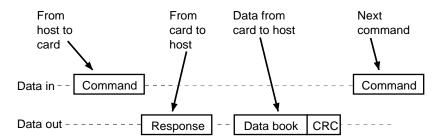

| 4.2.1. Data Read Format                          | 4-5  |

| 4.2.2. Data Write Format                         | 4-5  |

| 4.2.3. CSD Programming                           | 4-6  |

| 4.2.4. Erase                                     |      |

| 4.2.5. Write Protect Management                  |      |

| 4.2.6. Card Lock/Unlock                          |      |

| 4.3. Clock Control                               |      |

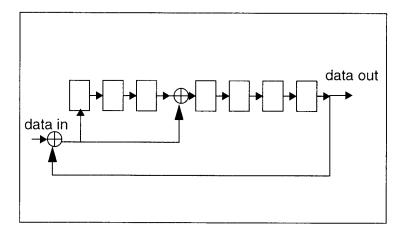

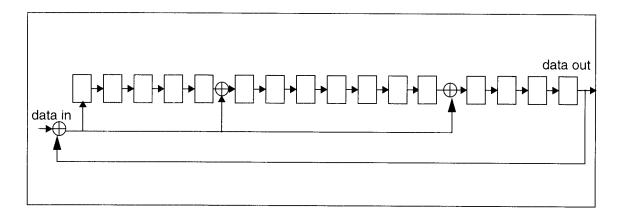

| 4.4. Cyclic Redundancy Codes (CRC)               |      |

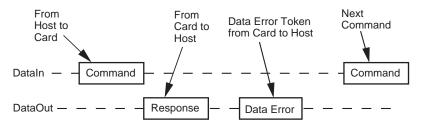

| 4.5. Error Conditions                            |      |

| 4.5.1. CRC and Illegal Command                   | 4-10 |

| 4.5.2. Read, Write and Erase Time-out Conditions | 4-10 |

| 4.6. Commands                                    | 4-10 |

| 4.6.1. Command Types                             | 4-10 |

| 4.6.2. Command Format.                           | 4-11 |

| 4.6.3. Command Classes                           | 4-11 |

| 4.6.4. Detailed Command Description              | 4-12 |

| 4.7. Device State Transition Table               |      |

| 4.8. Responses                                   | 4-17 |

| 4.8.1. Data Response                             | 4-18 |

| 4.9. Timings                                     | 4-18 |

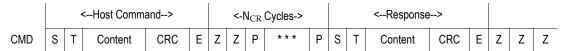

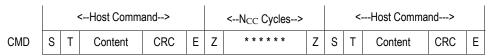

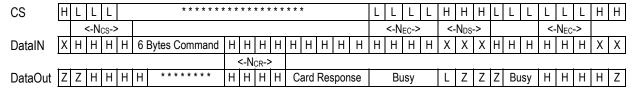

| 4.9.1. Command and Response                      | 4-19 |

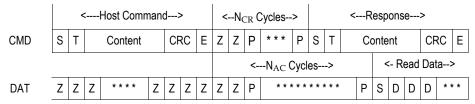

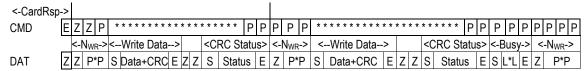

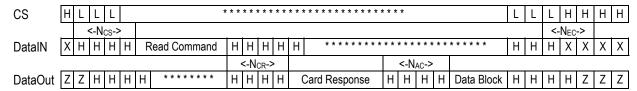

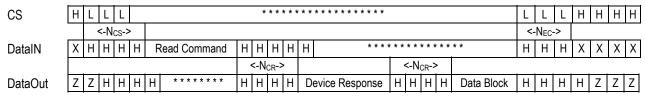

| 4.9.2. Data Read                                 | 4-20 |

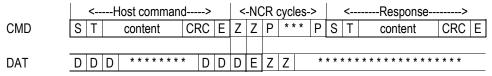

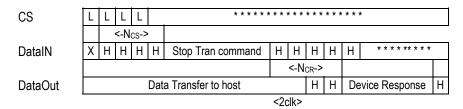

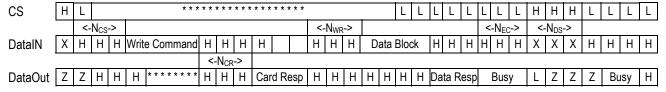

| 4.9.3. Data Write                                | 4-20 |

| 4.9.4. Timing Values                             | 4-22 |

| 5. SPI Protocol Definition                       | 5-1  |

| 5.1. SPI Bus Protocol                            |      |

| 5.1.1. Mode Selection                            | 5-1  |

| 5.1.2. Bus Transfer Protection                   | 5-2  |

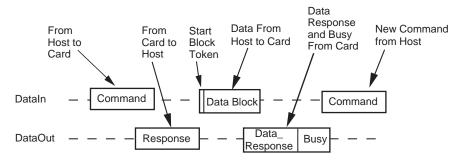

| 5.1.3. Data Read                                 | 5-2  |

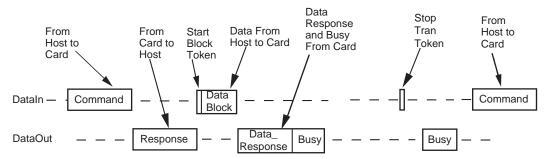

| 5.1.4. Data Write                                |      |

| 5.1.5. Erase and Write Protect Management        |      |

| 5.1.6. Read CID/CSD Registers                      | 5-5  |

|----------------------------------------------------|------|

| 5.1.7. Reset Sequence                              | 5-5  |

| 5.1.8. Clock Control                               | 5-5  |

| 5.1.9. Error Conditions                            | 5-6  |

| 5.1.9.1. CRC and Illegal Commands                  |      |

| 5.1.9.2. Read, Write and Erase Time-out Conditions |      |

| 5.1.10. Memory Array Partitioning                  | 5-6  |

| 5.1.11. Card Lock/Unlock                           | 5-7  |

| 5.2. SPI Command Set                               | 5-7  |

| 5.2.1. Command Format                              | 5-7  |

| 5.2.2. Command Classes                             | 5-7  |

| 5.2.2.1. Detailed Command Description              | 5-8  |

| 5.2.3. Responses                                   |      |

| 5.2.3.1. Format R1                                 |      |

| 5.2.3.2. Format R1b                                | 5-11 |

| 5.2.3.3. Format R2                                 |      |

| 5.2.3.4. Format R3                                 |      |

| 5.2.3.5. Data Response                             |      |

| 5.2.4. Data Tokens                                 |      |

| 5.2.5. Data Error Token                            |      |

| 5.2.6. Clearing Status Bits                        |      |

| 5.3. Device Registers                              |      |

| 5.4. SPI Bus Timing Diagrams                       |      |

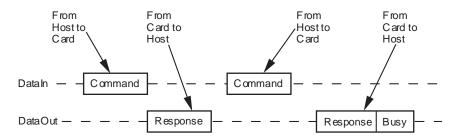

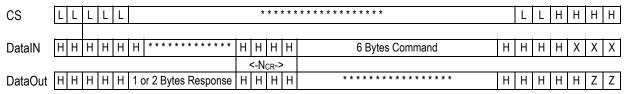

| 5.4.1. Command/Response                            |      |

| 5.4.2. Data Read                                   |      |

| 5.4.3. Data Write                                  | 5-16 |

| 5.4.4. Timing Values                               |      |

| 5.5. SPI Electrical Interface                      |      |

| 5.6. SPI Bus Operating Conditions                  |      |

| 5.7. Bus Timing                                    | 5-17 |

| Appendix A. Ordering Information                   | A-1  |

| Appendix B. Technical Support Services             | B-1  |

| Appendix C. SanDisk Worldwide Sales Offices        |      |

| Appendix D. Limited Warranty                       | D-1  |

This page intentionally left blank.

# 1. Introduction to the TriFlash

The SanDisk TriFlash is a very small flash storage device, designed specifically for storage applications that put a premium on small form factor, low power and low cost. Flash is the ideal storage medium for portable, battery-powered devices. It features low power consumption and is non-volatile, requiring no power to maintain the stored data. It also has a wide operating range for temperature, shock and vibration.

TriFlash is well suited to meet the needs of small, low power, electronic devices. With a form factor as small as 10 mm by 12 mm and 1.1 mm thick, TriFlash can be used in a wide variety of portable devices like mobile phones, digital audio players, car navigation devices, and voice recorders.

To support this wide range of applications, the TriFlash is offered with either the MultiMediaCard or Secure Digital (SD) protocol (see *TriFlash with Secure Digital Interface Product Manual*). The MultiMediaCard protocol is a simple 3-pin interface, which can be shared by the TriFlash and MultiMediaCards, providing the most compact memory interface available today. For compatibility with existing controllers, the TriFlash offers, in addition to these interfaces, an alternate communication protocol based on the SPI standard.

These interfaces allow for easy integration into any design, regardless of microprocessor used. All device and interface configuration data (such as maximum frequency, card identification, etc.) are stored on the device.

The TriFlash provides up to 1024 Mbits of memory using SanDisk Flash memory chips, which were designed by SanDisk especially for use in mass storage applications. In addition to the flash memory chip, the TriFlash includes an intelligent controller that manages interface protocols, and data storage and retrieval, as well as Error Correction Code (ECC) algorithms, defect handling and diagnostics, power management and clock control.

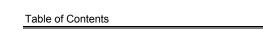

Figure 1-1. TriFlash with MultiMediaCard Interface Block Diagram

# 1.1. Scope

This document describes the key features and specifications of the TriFlash with the MultiMediaCard interface, as well as the information required to interface this product to a host system.

# 1.2. Product Models

The TriFlash is available in the capacities shown in Table 1-1.

Table 1-1. TriFlash Capacities

| MMC Model No. | Capacities |

|---------------|------------|

| SDAT1FAH-128  | 128 Mb     |

| SDBT1FAH-256  | 256 Mb     |

| SDBT1FCH-512  | 512 Mb     |

| SDBT1FCH-1024 | 1024 Mb    |

# 1.3. System Features

TriFlash provides the following system features:

- Up to 1024 Mbits of data storage.

- MultiMediaCard protocol compatible.

- Supports SPI Mode.

- Targeted for portable and stationary applications for data storage.

- Voltage range: 2.7-3.6V.

- Variable clock rate 0-20 MHz.

- Maximum data rate with up to 10 devices or cards.

- Correction of memory field errors.

- Built-in write protection features (permanent and temporary).

- · Comfortable erase mechanism.

- Standard pinout across all capacities.

- Single 3-wire bus for use with both the TriFlash and card.

The performance of the communication channel is described in Table 1-2.

Table 1-2. MultiMediaCard Bus /SPI Bus Comparison

| TriFlash Using MultiMediaCard Bus                            | TriFlash Using SPI Bus                                                                                        |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Three-wire serial data bus (Clock, Command, Data).           | Three-wire serial data bus (Clock, DataIn, DataOut) + device specific CS signal (hardwired device selection). |

| Up to 64k devices addressable by the bus protocol.           | Device selection via a hardware CS signal.                                                                    |

| Error-protected data transfer.                               | Optional. A non-protected data transfer mode is available.                                                    |

| Sequential and single/multiple block oriented data transfer. | Single or multiple block oriented data transfer.                                                              |

## 1.4. TriFlash with MultiMediaCard Interface Bus Standards

The SanDisk TriFlash is also fully compatible with the MultiMediaCard standard specification listed below:

The MultiMediaCard System Specification, Version 2.2

This specification may be obtained from:

MultiMediaCard Association 19672 Stevens Creek Blvd., Suite 404 Cupertino, CA 95014-2465 USA

Phone: 408-253-0441 Fax: 408-253-8811

Email: prophet2@mmca.org http://www.mmca.org

# 1.5. Functional Description

The SanDisk TriFlash contains a high level, intelligent subsystem as shown in the block diagram, Figure 1-1. This intelligent (microprocessor) subsystem provides many capabilities not found in other types of devices. These capabilities include:

- Host independence from details of erasing and programming flash memory.

- Sophisticated system for managing defects (analogous to systems found in magnetic disk drives).

- Sophisticated system for error recovery including a powerful error correction code (ECC).

- Power management for low power operation.

### 1.5.1. Flash Technology Independence

The 512-byte sector size of the TriFlash is the same as that in an IDE magnetic disk drive. To write or read a sector (or multiple sectors), the host The host software then waits for the command to complete. The host software does not get involved in the details of how the flash memory is erased, programmed or read. This is extremely important as flash devices are expected to get more and more complex in the future. Because the TriFlash uses an intelligent on-board controller, the host system software will not require changing as new flash memory evolves. In other words, systems that support the TriFlash today will be able to access future SanDisk TriFlash devices built with new flash technology without having to update or change host software.

#### 1.5.2. Defect and Error Management

The TriFlash contains a sophisticated defect and error management system. This system is analogous to the systems found in magnetic disk drives and in many cases offers enhancements. For instance, disk drives do not typically perform a read after write to confirm the data is written correctly because of the performance penalty that would be incurred. The TriFlash does a read after write under margin conditions to verify that the data is written correctly. In the rare case that a bit is found to be defective, the TriFlash replaces this bad bit with a spare bit within the sector header. If necessary, the TriFlash will even replace the entire sector with a spare sector. This is completely transparent to the host and does not consume any user data space.

The TriFlash device's soft error rate specification is much better than the magnetic disk drive specification. In the extremely rare case a read error does occur, the TriFlash has innovative algorithms to recover the data. This is similar to using retries on a disk drive but is much more sophisticated. The last line of defense is to employ a powerful ECC to correct the data. If ECC is used to recover data, defective bits are replaced with spare bits to ensure they do not cause any future problems. These defect and error management systems coupled with the solid-state construction give the TriFlash unparalleled reliability.

#### 1.5.3. Endurance

The SanDisk TriFlash has an endurance specification for each sector of 100,000 writes (reading a logical sector is unlimited) under typical conditions. This far exceeds what is needed in nearly all applications of TriFlash devices. Even very heavy use of the TriFlash in cellular phones, personal communicators, pagers and voice recorders will use only a fraction of the total endurance over the typical device's lifetime. For instance, it would take over 34 years to wear out an area on the TriFlash on which a file of any size (from 512 bytes to maximum capacity) was rewritten 3 times per hour, 8 hours a day, 365 days per year. With typical applications, the endurance limit is not of any practical concern to the vast majority of users.

#### 1.5.4. Automatic Sleep Mode

A unique feature of the SanDisk TriFlash (and other SanDisk products) is automatic entrance and exit from sleep mode. Upon completion of an operation, the TriFlash will enter the sleep mode to conserve power if no further commands are received within 5msec. The host does not have to take any action for this to occur. In most systems, the TriFlash is in sleep mode except when the host is accessing it, thus conserving power. When the host is ready to access the TriFlash and it is in sleep mode, any command issued to the TriFlash will cause it to exit sleep and respond.

#### 1.5.5. TriFlash MultiMediaCard Mode

The following sections provide valuable information for TriFlash in MultiMediaCard mode.

#### 1.5.5.1. MultiMediaCard Standard Compliance

The TriFlash with MultiMediaCard interface is fully compliant with MultiMediaCard Standard Specification, version 2.2. The structure of the Card Specific Data (CSD) register is compliant with CSD structure version 1.1.

### 1.5.5.2. Negotiating Operation Conditions

The TriFlash supports the operation condition verification sequence defined in the MultiMediaCard Standard Specifications. Should the TriFlash host define an operating voltage range, which is not supported by the TriFlash, it will put itself in an inactive state and ignore any bus communication. The only way to get the device out of the inactive state is by powering it down and up again. In addition, the host can explicitly send the device to the inactive state by using the GO\_INACTIVE\_STATE command.

#### 1.5.5.3. Device Acquisition and Identification

The MultiMediaCard bus is a single master (TriFlash host) and multi-slaves (devices) bus. The host can query the bus and find out how many devices of which type are currently connected. The TriFlash's CID register is preprogrammed with a unique card identification number that is used during the acquisition and identification procedure.

In addition, the TriFlash host can read the device's CID register using the READ\_CID command. The CID register is programmed during the TriFlash testing and formatting procedure, on the manufacturing floor. The TriFlash host can only read this register and not write to it.

#### 1.5.5.4. Device Status

TriFlash status is stored in a 32-bit status register which is sent as the data field in the device response to host commands. The Status register provides information about the device's current state and completion codes for the last host command. The device status can be explicitly read (polled) with the SEND STATUS command.

## 1.5.5.5. Memory Array Partitioning

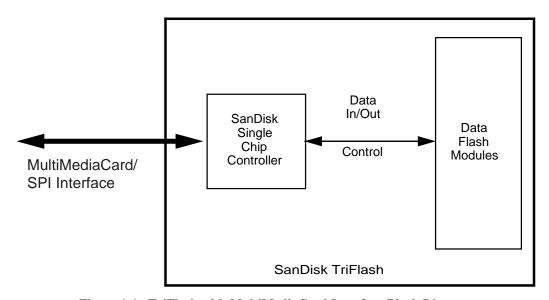

Although the TriFlash memory space is byte addressable with addresses ranging from 0 to the last byte, it is not a simple byte array but divided into several structures as follows:

- Memory bytes are grouped into 512 byte blocks called sectors. Every block can be read, written and erased individually.

- Sectors are grouped into erase groups of 16 or 32 sectors depending on device size. Any combination of sectors within one group, or any combination of erase groups can be erased in a single erase command. A write command implicitly erases the memory before writing new data into it. An explicit erase command can be used for pre-erasing memory, which will speed up the next write operation.

- Erase groups are grouped into Write Protect Groups (WPG) of 32 erase groups. The write/erase access to each WPG can be limited individually. A diagram of the memory structure hierarchy is shown in Figure 1-2.

The number of various memory structures for the different TriFlash devices are summarized in Table 1-3. The last (highest in address) WPG will be smaller and contain less than 32 erase groups.

Figure 1-2. Memory Array Partitioning

Table 1-3. TriFlash Memory Array Structures Summary

| Part Number   | Bits   | Sector  | Erase Group Size<br>(Sectors) | Number of<br>Erase Groups | Write Protect Group<br>Size (erase groups) | Number of Write<br>Protect Groups |

|---------------|--------|---------|-------------------------------|---------------------------|--------------------------------------------|-----------------------------------|

| SDBT1FCH-1024 | 1024Mb | 250,880 | 32                            | 7,840                     | 32                                         | 245                               |

| SDBT1FCH-512  | 512Mb  | 125,440 | 32                            | 3,920                     | 32                                         | 123                               |

| SDBT1FAH-256  | 256Mb  | 62,720  | 32                            | 1,960                     | 32                                         | 62                                |

| SDAT1FAH-128  | 128Mb  | 31,360  | 32                            | 980                       | 32                                         | 31                                |

## 1.5.5.6. Read and Write Operations

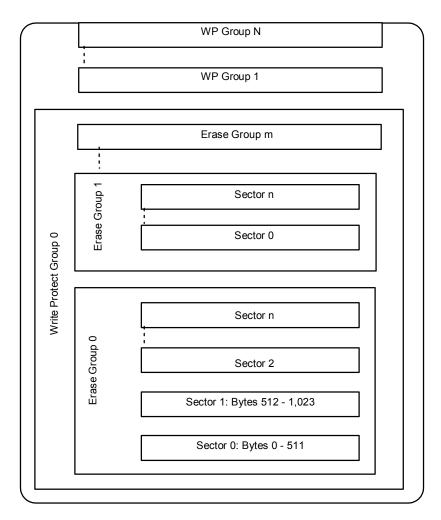

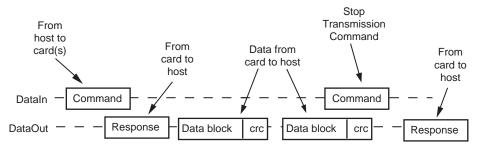

The TriFlash supports three read/write modes as shown in Figure 1-3.

Figure 1-3. Data Transfer Formats

#### Single Block Mode

In this mode, the host reads or writes one data block in a pre-specified length. The data block transmission is protected with 16-bit CRC, which is generated by the sending unit and checked by the receiving unit.

The block length for read operations is limited by the device sector size (512 bytes), but can be as small as a single byte. Misalignment is not allowed. Every data block must be contained in a single physical sector.

The block length for write operations must be identical to the sector size and the start address aligned to a sector boundary.

#### **Multiple Block Mode**

This mode is similar to the single block mode, but the host can read/write multiple data blocks (all have the same length), which will be stored or retrieved from contiguous memory addresses starting at the address specified in the command.

The operation is terminated with a stop transmission command.

Misalignment and block length restrictions apply to multiple blocks as well, and are identical to the single block read/write operations.

#### 1.5.5.7. Data Protection in the TriFlash

Every sector is protected with an Error Correction Code (ECC). The ECC is generated (in the device) when the sectors are written and validated when the data is read. If defects are found, the data is corrected prior to transmission to the host.

#### 1.5.5.8. Erase

The smallest erasable unit in the TriFlash is a sector. In order to speed up the erase procedure, multiple sectors can be erased at the same time. To facilitate selection, a first command with the starting address is followed by a second command with the final address, and all sectors within this range are selected for erase.

#### 1.5.5.9. Write Protection

Two device level write protection options, permanent and temporary, are available. Both can be set using the PROGRAM\_CSD command (see Section 4.2.2). The permanent write protect bit, once set, cannot be cleared. This feature is implemented in the TriFlash controller firmware and not with a physical OTP cell.

#### 1.5.5.10. Copy Bit

The content of a TriFlash can be marked as an original or a copy using the copy bit in the CSD register. Once the Copy bit is set (marked as a copy) it cannot be cleared. The Copy bit of the TriFlash is programmed (during test and formatting on the manufacturing floor) as a copy. The TriFlash can be purchased with the copy bit set (copy) or cleared, indicating the device is a master. This feature is implemented in the TriFlash controller firmware and not with a physical OTP cell.

#### 1.5.5.11. The CSD Register

All the configuration information of the TriFlash is stored in the CSD register. The MSB bytes of the register contain manufacturer data. The two least significant bytes contain the host controlled data: the device Copy and write protection, the user file format indication, and the user ECC register.

The host can read the CSD register and alter the host-controlled data bytes using the SEND\_CSD and PROGRAM\_CSD commands (see Section 4.2.2).

#### 1.5.6. TriFlash—SPI Mode

The SPI mode is a secondary communication protocol for TriFlash devices. This mode is a subset of the MultiMediaCard bus protocol, designed to communicate with an SPI channel, commonly found in Motorola's (and lately a few other vendors') microcontrollers.

#### 1.5.6.1. Negotiating Operating Conditions

The operating condition negotiation function of the MultiMediaCard bus is not supported in SPI mode. The host must work within the valid voltage range (2.7 to 3.6 volts) of the card.

## 1.5.6.2. Device Acquisition and Identification

The host must know the number of devices currently connected on the bus. Specific device selection is done via the CS signal. The internal pullup resistor on the CD line may be used for device detection (insertion/removal).

#### 1.5.6.3. Device Status

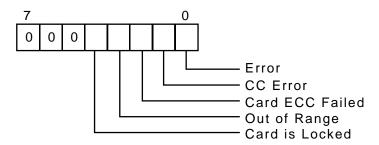

In SPI mode, only 16 bits (containing the errors relevant to SPI mode) can be read out of the 32-bit TriFlash status register.

### 1.5.6.4. Memory Array Partitioning

Memory partitioning in SPI mode is equivalent to MultiMediaCard Bus mode. All read and write commands are byte addressable with the limitations given in section 1.5.7.5 above.

#### 1.5.6.5. Read and Write Operations

In SPI mode, both single and multiple block data transfer modes are supported.

#### 1.5.6.6. Data Transfer Rate

Same as for the MultiMediaCard mode when the device is operating in single block read/write mode.

## 1.5.6.7. Data Protection in the TriFlash

Same as for the MultiMediaCard Bus mode.

#### 1.5.6.8. Erase

Same as in MultiMediaCard Bus mode.

### 1.5.6.9. Write Protection

Same as in MultiMediaCard Bus mode.

# 2. Product Specifications

For all the following specifications, values are defined at ambient temperature and nominal supply voltage unless otherwise stated.

# 2.1. System Environmental Specifications

Table 2-1. System Environmental Specifications

|                                  | _                            |                                                        |

|----------------------------------|------------------------------|--------------------------------------------------------|

| Temperature                      | Operating:<br>Non-Operating: | -25° C to 85° C<br>-40° C to 85° C                     |

| Humidity                         | Operating: Non-Operating:    | 8% to 95%, non-condensing<br>8% to 95%, non-condensing |

| ESD Protection                   |                              | ± 2kV, Human body model                                |

| Vibration                        | Operating:<br>Non-Operating: | 15 G peak to peak max.<br>15 G peak to peak max.       |

| Shock                            | Operating:<br>Non-Operating: | 1,000 G max.<br>1,000 G max.                           |

| Altitude (relative to sea level) | Operating:<br>Non-Operating: | 80,000 feet max.<br>80,000 feet max.                   |

# 2.2. Typical Power Requirements

**Table 2-2. Power Requirements**

| VDD (ripple: max, 60 mV peak to peak) | 2.7 V-3.6 V |

|---------------------------------------|-------------|

|                                       |             |

(Ta = -25 - 85C)

|                                                                                 | @ VDD = 2.7 V               | @ VDD = 3.6 V               |

|---------------------------------------------------------------------------------|-----------------------------|-----------------------------|

| Operating current (maximum rates). Fclk = 20 MHz, 0.5 MByte/s. Read/Write speed | Read: 30 mA<br>Write: 35 mA | Read: 40 mA<br>Write: 45 mA |

(Ta = -25 - 85C)

|               |         | Typical | Maximum |

|---------------|---------|---------|---------|

| Claan Current | @ 2.7 V | 40 uA   | 120 uA  |

| Sleep Current | @3.3 V  | 50 uA   | 150 uA  |

# 2.3. System Performance

Table 2-3. System Performance<sup>1</sup>

|                                 | Typical           | Maximum            |

|---------------------------------|-------------------|--------------------|

| Block Read Access Time          |                   |                    |

| Binary Products<br>MLC Products | 1.5msec<br>10msec | 15msec<br>100msec  |

| Block Write Access Time         |                   |                    |

| Binary Products<br>MLC Products | 24msec<br>40msec  | 240msec<br>400msec |

| CMD1 to Ready (after power up)  | 50msec            | 500msec            |

| Sleep to Ready                  | 1msec             | 2msec              |

# 2.4. System Reliability and Maintenance

Table 2-4. System Reliability and Maintenance Specifications

| MTBF                   | > 1,000,000 hours                                 |

|------------------------|---------------------------------------------------|

| Preventive Maintenance | None                                              |

| Data Reliability       | < 1 non-recoverable error in 1014 bits read       |

| Endurance              | ≥ 100,000 erase/program cycles per block, typical |

# 2.5. Physical Specifications

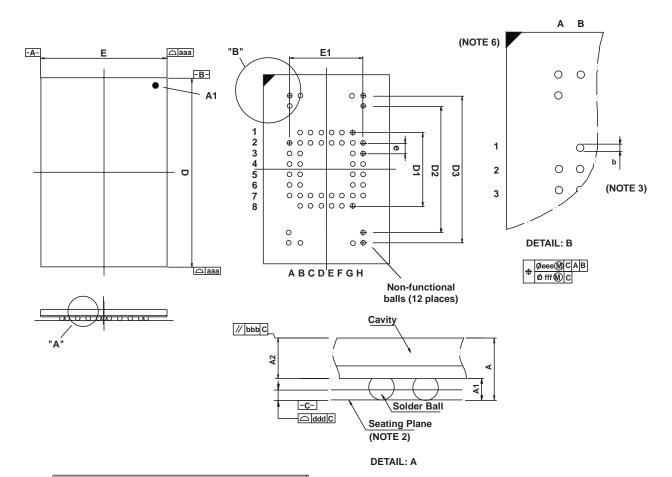

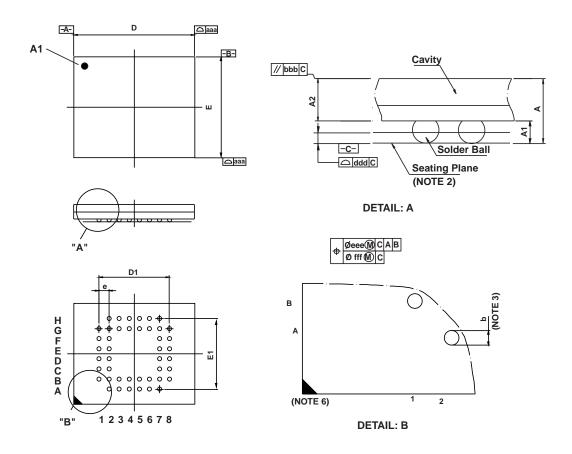

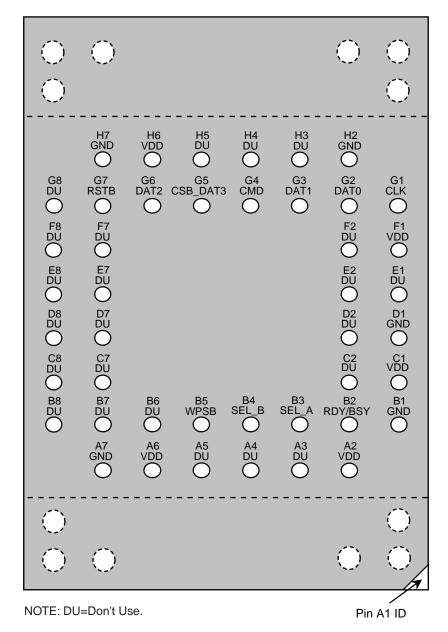

See Figures 2-1 and 2-2 for the physical specifications and dimensions and Figure 2-3 for pin definitions.

<sup>&</sup>lt;sup>1</sup> All values quoted are under the following conditions:

a) Voltage range: 2.7 V to 3.6 V.

b) Temperature range: -25° C to 85° C.

c) Are independent of the TriFlash clock frequency.

| Dimension in mm |       |       | Dimension in inch |       |       |       |  |

|-----------------|-------|-------|-------------------|-------|-------|-------|--|

| Symbol          | MIN   | NOM   | MAX               | Min   | NOM   | MAX   |  |

| Α               |       |       | 1.10              |       |       | 0.043 |  |

| A1              | 0.32  | 0.35  | 0.38              | 0.013 | 0.014 | 0.015 |  |

| A2              | 0.62  | 0.67  | 0.72              | 0.024 | 0.026 | 0.028 |  |

| D               | 17.90 | 18.00 | 18.10             | 0.705 | 0.709 | 0.713 |  |

| E               | 11.90 | 12.00 | 12.10             | 0.469 | 0.472 | 0.476 |  |

| D1              |       | 7.00  |                   |       | 0.276 |       |  |

| D2              |       | 11.00 |                   |       | 0.433 |       |  |

| D3              |       | 13.00 |                   |       | 0.512 |       |  |

| E1              |       | 7.00  |                   |       | 0.276 |       |  |

| е               |       | 1.00  |                   |       | 0.039 |       |  |

| b               | 0.40  | 0.45  | 0.50              | 0.016 | 0.018 | 0.020 |  |

| aaa             |       | 0.10  |                   | 0.004 |       |       |  |

| bbb             |       | 0.10  |                   | 0.004 |       |       |  |

| ddd             | 0.15  |       |                   | 0.006 |       |       |  |

| eee             | 0.25  |       |                   | 0.010 |       |       |  |

| fff             | 0.10  |       |                   | 0.004 |       |       |  |

| MD/ME           |       | 12/11 |                   |       | 12/11 |       |  |

#### NOTE:

- 1. Controlling Dimension: Millimeter.

- 2. Primary Datum C and seating plane are defined by the spherical crowns of the solder balls.

- 3. Dimensions b is measured at the maximum solder ball diameter, parallel to Primary Datum C.

- 4. There shall be a minimum clearance of 0.25mm between the edge of the solder ball and the body edge.

- 5. Reference document: JEDEC MO-205.

- 6. The pattern of Pin 1 Fiducial is for reference only.

- 7. All numbers are in mm.

- 8. All numbers are typical unless otherwise stated.

Figure 2-1. TriFlash Physical Specifications—18 X 12mm Package

| Dimension in mm |       |       | Dimension in inch |       |       |       |

|-----------------|-------|-------|-------------------|-------|-------|-------|

| Symbol          | MIN   | NOM   | MAX               | Min   | NOM   | MAX   |

| Α               |       |       | 1.10              |       |       | 0.043 |

| A1              | 0.32  | 0.35  | 0.38              | 0.013 | 0.014 | 0.015 |

| A2              | 0.62  | 0.67  | 0.72              | 0.024 | 0.026 | 0.028 |

| D               | 11.90 | 12.00 | 12.10             | 0.469 | 0.472 | 0.476 |

| E               | 9.90  | 10.00 | 10.10             | 0.390 | 0.394 | 0.398 |

| D1              |       | 7.00  |                   |       | 0.276 |       |

| E1              |       | 7.00  |                   |       | 0.276 |       |

| е               |       | 1.00  |                   |       | 0.039 |       |

| b               | 0.40  | 0.45  | 0.50              | 0.016 | 0.018 | 0.020 |

| aaa             |       | 0.10  |                   |       | 0.004 |       |

| bbb             |       | 0.10  |                   | 0.004 |       |       |

| ddd             | 0.15  |       |                   | 0.006 |       |       |

| eee             | 0.25  |       |                   | 0.010 |       |       |

| fff             | 0.10  |       |                   | 0.004 |       |       |

| MD/ME           |       | 8/8   | ·                 | 8/8   |       |       |

## NOTE:

- 1. Controlling Dimension: Millimeter.

- 2. Primary Datum C and seating plane are defined by the spherical crowns of the solder balls.

- 3. Dimensions b is measured at the maximum solder ball diameter, parallel to Primary Datum C.

- 4. There shall be a minimum clearance of 0.25mm between the edge of the solder ball and the body edge.

- 5. Reference document: JEDEC MO-205.

- 6. The pattern of Pin 1 Fiducial is for reference only.

Figure 2-2. TriFlash Physical Specifications—12 X 10mm Package

Figure 2-3. TriFlash Pin Definitions (Top View)

# 3. TriFlash Interface Description

# 3.1. General Description of Pins and Registers

The TriFlash is a BGA package with 44 core balls (see Figure 2-3). The host is connected to the TriFlash using the 11 interface connections shown in Tables 3-1 and 3-2, plus power and ground balls.

# 3.1.1. Pin Assignments in MultiMediaCard Mode

Table 3-1. MultiMediaCard Pin Definition

| Pin#               | Name            | Type <sup>1</sup> | Function              | Comment          |

|--------------------|-----------------|-------------------|-----------------------|------------------|

| H6, F1, C1, A2, A6 | $V_{DD}$        | S                 | Supply Voltage        |                  |

| H7, H2, D1, B1, A7 | V <sub>SS</sub> | S                 | Supply Voltage Ground |                  |

| G2                 | DAT0            | I/O               | Data Line             |                  |

| G3                 | DAT1            | I/O               | Unused                | Pull up to VDD   |

| G6                 | DAT2            | I/O               | Unused                | Pull up to VDD   |

| G5                 | DAT3            | I/O               | Unused                | Pull up to VDD   |

| G1                 | CLK             | I                 | Clock                 |                  |

| G4                 | CMD             | I/O               | Command/Response      |                  |

| B5                 | WPSB            | I                 | Write Protect         |                  |

| G7                 | RSTB            | I                 | Reset (Active low)    |                  |

| B2                 | RDY/BSY         | 0                 | Ready/Busy Interrupt  |                  |

| В3                 | SEL_A           | I                 | Defines I/F           | Pull down to VSS |

| B4                 | SEL_B           | I                 | Defines I/F           | Pull down to VSS |

\_

<sup>&</sup>lt;sup>1</sup> S=power supply; I=input; O=output using push-pull drivers.

# 3.1.2. Pin Assignments in SPI Mode

Table 3-2. SPI Bus Mode Pin Definition

| Pin#               | Name     | Type <sup>1</sup> | Function                         | Comment          |

|--------------------|----------|-------------------|----------------------------------|------------------|

| H6, F1, C1, A2, A6 | $V_{DD}$ | S                 | Supply Voltage                   |                  |

| H7, H2, D1, B1, A7 | Vss      | S                 | Supply Voltage Ground            |                  |

| G2                 | DataOut  | I/O               | Device to Host Data and Status   |                  |

| G3                 | DAT1     | I/O               | Unused                           | Pull up to VDD   |

| G6                 | DAT2     | I/O               | Unused                           | Pull up to VDD   |

| G5                 | CS       | I                 | Chip Select (Active low)         |                  |

| G1                 | CLK      | 1                 | Clock                            |                  |

| G4                 | DataIn   | 1                 | Host to Device Commands and Data |                  |

| B5                 | WPSB     | 1                 | Write Protect                    |                  |

| G7                 | RSTB     | I                 | Reset (Active low)               |                  |

| B2                 | RDY/BSY  | 0                 | Ready/Busy Interrupt             |                  |

| В3                 | SEL_A    | I                 | Defines I/F                      | Pull down to VSS |

| B4                 | SEL_B    | I                 | Defines I/F                      | Pull down to VSS |

## 3.1.3. Registers

Each device has a set of information registers. A detailed description is given in section 4.5.

Table 3-3. TriFlash with MultiMediaCard Registers

| Name             | Width | Description                                                                                                                                  |

|------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CID              | 128   | Card identification number: individual device number for identification.                                                                     |

| RCA <sup>2</sup> | 16    | Relative card address: local system address of a device, dynamically suggested by the device and approved by the host during initialization. |

| CSD              | 128   | Card specific data: information about the device operation conditions.                                                                       |

| OCR              | 32    | Operation Condition Register.                                                                                                                |

The host may reset the devices by switching the power supply off and on again. The device has its own power-on detection circuitry that puts the device into an idle state after the power-on. The device can also be reset by sending the GO\_IDLE (CMD0) command, or by providing a negative pulse on the RESET pin.

<sup>&</sup>lt;sup>1</sup> S=power supply; I=input; O=output using push-pull drivers.

<sup>&</sup>lt;sup>2</sup> The RCA register is not used (available) in SPI Mode.

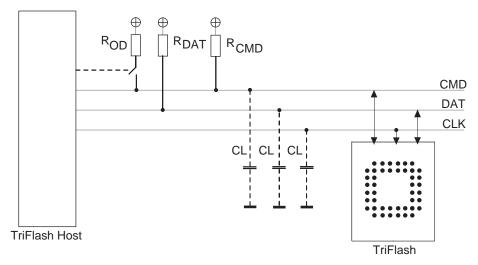

# 3.2. MultiMediaCard Bus Topology

The MultiMediaCard Bus has three communication lines and power and ground:

- **CMD**—Command is a bi-directional signal. Host and device drivers are operating in two modes, open drain and push pull.

- **DAT**—Data is a bi-directional signal. Host and device drivers are operating in push pull mode.

- CLK—Clock is a host to device signal. CLK operates in push pull mode.

- **VDD**—VDD is the power supply line for all devices.

- VSS—VSS are ground lines.

Figure 3-1. MultiMediaCard Bus Circuitry Diagram

The  $R_{OD}$  is switched on and off by the host synchronously to the open-drain and push-pull mode transitions.  $R_{DAT}$  and  $R_{CMD}$  are pull-up resistors protecting the CMD and the DAT line against bus floating when all device drivers are in a hi-impedance mode.

A constant current source can replace the  $R_{\rm OD}$  in order to achieve better performance (constant slopes for the signal rising and falling edges). If the host does not allow the switchable  $R_{\rm OD}$  implementation, a fix  $R_{\rm CMD}$  can be used. Consequently the maximum operating frequency in the open drain mode has to be reduced in this case.

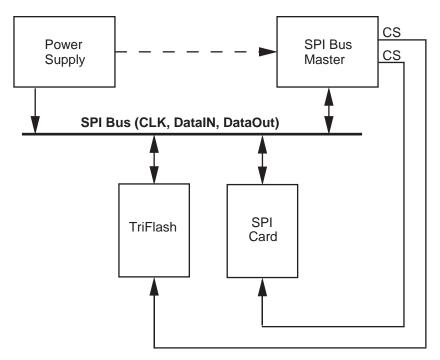

# 3.3. SPI Bus Topology

The TriFlash SPI interface is compatible with SPI hosts available on the market. As with any other SPI device the TriFlash SPI channel consists of the following four signals:

- CS—Host to device Chip Select signal.

- CLK—Host to device clock signal

- **DataIn**—Host to device data signal.

- **DataOut**—Device to host data signal.

Another SPI common characteristic, which is implemented in the MultiMediaCard bus as well, is byte transfers. All data tokens are multiples of 8 bit bytes and always byte aligned to the CS signal.

The SPI standard defines the physical link only and not the complete data transfer protocol. In SPI Bus mode, the TriFlash uses a subset of the MultiMediaCard protocol and command set.

The TriFlash identification and addressing algorithms are replaced by a hardware Chip Select (CS) signal. A device (slave) is selected, for every command, by asserting (active low) the CS signal (see Figure 3-2).

The CS signal must be continuously active for the duration of the SPI transaction (command, response and data). The only exception is device programming time. At this time the host can de-assert the CS signal without affecting the programming process.

The bi-directional CMD and DAT lines are replaced by unidirectional DataIn and DataOut signals. This eliminates the ability of executing commands while data is being read or written. An exception is the multi read/write operations. The Stop Transmission command can be sent during data read. In the multi block write operation a Stop Transmission token is sent as the first byte of the data block.

Figure 3-2. SPI Bus System

# 3.4. Electrical Interface

The following sections provide valuable information for TriFlash's electrical interface.

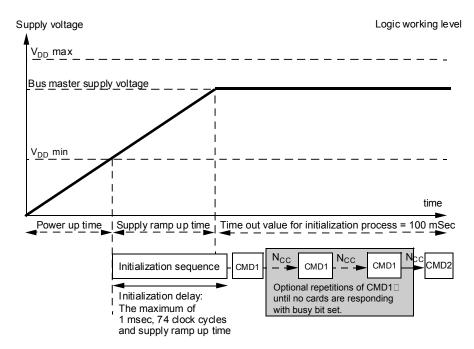

#### 3.4.1. Power-up

The power up of the bus is handled locally in each TriFlash and in the bus master.

Figure 3-3. Power-up Diagram

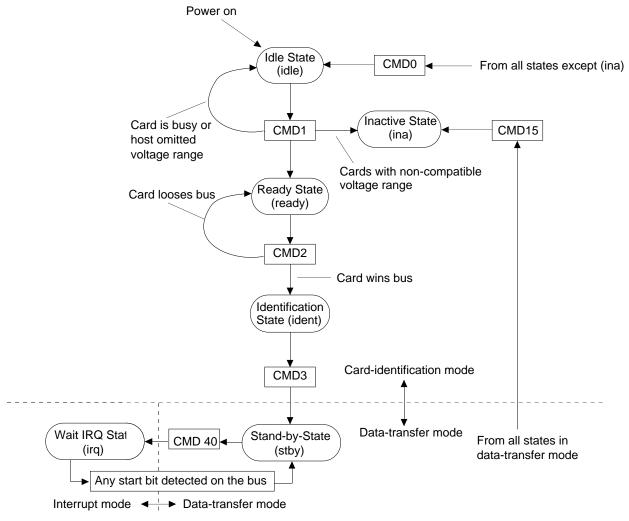

After power up the TriFlash enters the *idle state*. During this state the TriFlash ignores all bus transactions until CMD1 is received.

CMD1 is a special synchronization command used to negotiate the operation voltage range and to poll the devices until they are out of their power-up sequence. Besides the operation voltage profile of the devices, the response to CMD1 contains a busy flag, indicating that the device is still working on its power-up procedure and is not ready for identification. This bit informs the host that at least one device is not ready. The host has to wait (and continue to poll the devices) until this bit is cleared. The TriFlash shall complete its initialization procedure within 500msec.

Getting individual devices, as well as the whole TriFlash system, out of *idle state* is the responsibility of the bus master. Since the power up time and the supply ramp up time depend on application parameters such as the maximum number of devices, the bus length and the power supply unit, the host must ensure that the power is built up to the operating level (the same level which will be specified in CMD1) before CMD1 is transmitted.

After power up, the host starts the clock and sends the initialising sequence on the CMD line. This sequence is a contiguous stream of logical '1's. The sequence length is the maximum of 1msec, 74 clocks or the supply ramp-up time. The additional 10 clocks (over the 64 clocks after what the device should be ready for communication) are provided to eliminate power-up synchronization problems.

## 3.4.2. Bus Operating Conditions

SPI Mode bus operating conditions are identical to MultiMediaCard mode bus operating conditions. The chip select (CS) signal timing is identical to the input signal timing (see Figure 3-5).

Table 3-4. Power Supply Voltage

|                                           |                 |              | _       |      |                                 |

|-------------------------------------------|-----------------|--------------|---------|------|---------------------------------|

|                                           | Ge              | neral        |         |      |                                 |

| Parameter                                 | Symbol          | Min.         | Max.    | Unit | Remark                          |

| Peak voltage on all lines                 |                 | -0.3         | VDD+0.3 | V    |                                 |

|                                           | All             | Inputs       |         |      | •                               |

| Input Leakage Current                     |                 | -10          | 10      | μΑ   |                                 |

|                                           | All C           | Outputs      |         |      | •                               |

| Output Leakage Current                    |                 | -10          | 10      | μΑ   |                                 |

|                                           | Power Su        | pply Voltage |         |      |                                 |

| Parameter                                 | Symbol          | Min.         | Max.    | Unit | Remark                          |

| Supply Voltage                            | V <sub>DD</sub> | 2.7          | 3.6     | V    |                                 |

| Supply voltage differentials (Vss1, Vss2) |                 | -0.3         | 0.3     | V    |                                 |

| Power up Time                             |                 |              | 250     | mS   | From 0V to V <sub>DD</sub> Min. |

## **Bus Signal Line Load**

The total capacitance CL of the CLK line of the bus is the sum of the bus master capacitance CHOST, the bus capacitance CBUS itself and the capacitance  $C_{DEV}$  of each device connected to this line:

$$CL = CHOST + CBUS + N*C_{DEV}$$

Where N is the number of connected devices. Requiring the sum of the host and bus capacitances not to exceed 30 pF for up to 10 devices, and 40 pF for up to 30 devices, the values in Table 3-5 must not be exceeded.

Table 3-5. Signal Line's Load

| Parameter                                | Symbol                               | Min. | Max. | Unit | Remark                              |

|------------------------------------------|--------------------------------------|------|------|------|-------------------------------------|

| Pull-up resistance                       | R <sub>CMD</sub><br>R <sub>DAT</sub> | 10   | 100  | kΩ   | To prevent bus floating             |

| Bus signal line capacitance              | CL                                   |      | 250  | pF   | f <sub>PP</sub> ≤ 5 MHz, 21 devices |

| Bus signal line capacitance              | CL                                   |      | 100  | pF   | f <sub>PP</sub> ≤ 20 MHz, 7 devices |

| Single device capacitance                | C <sub>DEV</sub>                     |      | 10   | pF   |                                     |

| Maximum signal line inductance           |                                      |      | 16   | nH   | f <sub>PP</sub> ≤ 20 MHz            |

| Pull-up resistance inside device (pin 1) | R <sub>DAT3</sub>                    | 10   | 90   | kΩ   | May be used for device detection.   |

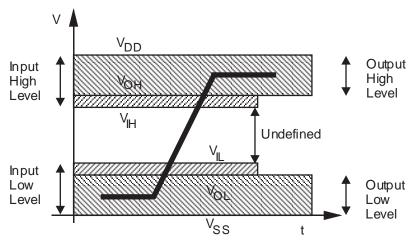

## 3.4.3. Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

Figure 3-4. Bus Signal Levels

To meet the requirements of the JEDEC specification JESD8-1A, the device input and output voltages shall be within the specified ranges in Table 3-6 for any VDD of the allowed voltage range.

Parameter Symbol Min. Max. Unit Conditions Output HIGH voltage VOH 0.75\*VDD ٧ IOH=-100 μA @V<sub>DD</sub> (min.) Output LOW voltage VOL ٧ 0.125\*VDD IOL=100 μA @V<sub>DD</sub> (min.) ٧ VIH VDD + 0.3 Input HIGH voltage 0.625\*VDD VIL VSS-0.3 ٧ Input LOW voltage 0.25\*VDD

Table 3-6. Input and Output Voltages

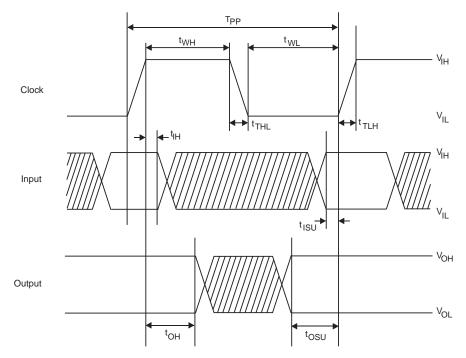

# 3.4.4. Bus Timing

Figure 3-5. Timing Diagram Data Input/Output Referenced to Clock

Table 3-7. Bus Timing

| Parameter                                   | Symbol             | Min.            | Max.                         | Unit    | Remark                                   |  |  |  |

|---------------------------------------------|--------------------|-----------------|------------------------------|---------|------------------------------------------|--|--|--|

| Clock C                                     | LK (All values are | referred to min | . (V <sub>IH</sub> ) and max | . (Vı∟) |                                          |  |  |  |

| Clock Frequency Data Transfer<br>Mode (PP)  | f <sub>PP</sub>    | 0               | 20                           | MHz     | $C_L \le 100 \text{ pF}$<br>(10 devices) |  |  |  |

| Clock Frequency Identification<br>Mode (OD) | f <sub>OD</sub>    | 0               | 400                          | kHz     | C <sub>L</sub> ≤ 250 pF<br>(30 devices)  |  |  |  |

| Clock Low Time                              | twL                | 10              |                              | ns      | C <sub>L</sub> ≤ 100 pF<br>(10 devices)  |  |  |  |

| Clock High Time                             | twн                | 10              |                              | ns      | $C_L \le 100 \text{ pF}$<br>(10 devices) |  |  |  |

| Clock Rise Time                             | t <sub>TLH</sub>   |                 | 10                           | ns      | $C_L \le 100 \text{ pF}$<br>(10 devices) |  |  |  |

| Clock Fall Time                             | tтнL               |                 | 10                           | ns      | C <sub>L</sub> ≤ 100 pF<br>(10 devices)  |  |  |  |

| Clock Low Time                              | twL                | 50              |                              | ns      | C <sub>L</sub> ≤ 250 pF<br>(30 devices)  |  |  |  |

| Clock High Time                             | twн                | 50              |                              | ns      | C <sub>L</sub> ≤ 250 pF<br>(30 devices)  |  |  |  |

| Clock Rise Time                             | tт∟н               |                 | 50                           | ns      | C <sub>L</sub> ≤ 250 pF<br>(30 devices)  |  |  |  |

| Parameter                           | Symbol                               | Min. | Max. | Unit | Remark                                  |  |  |  |  |

|-------------------------------------|--------------------------------------|------|------|------|-----------------------------------------|--|--|--|--|

| Clock Fall Time                     | tтнL                                 |      | 50   | ns   | C <sub>L</sub> ≤ 250 pF<br>(30 devices) |  |  |  |  |

| Inputs CMD, DAT (referenced to CLK) |                                      |      |      |      |                                         |  |  |  |  |

| Input set-up time                   | t <sub>isu</sub>                     | 3    |      | ns   |                                         |  |  |  |  |

| Input hold time                     | t <sub>IH</sub>                      | 3    |      | ns   |                                         |  |  |  |  |

|                                     | Outputs CMD, DAT (referenced to CLK) |      |      |      |                                         |  |  |  |  |

| Output set-up time                  | tosu                                 | 5    |      | ns   |                                         |  |  |  |  |

| Output hold time                    | tон                                  | 5    |      | ns   |                                         |  |  |  |  |

## 3.4.5. TriFlash-Specific Functions

The following sections list the TriFlash-specific functions.

### 3.4.5.1. Ready/Busy Function [Output]

The RDY/BSY pin indicates "0" if the TriFlash is in "Busy" condition. Busy condition is a period where the data paths of the TriFlash are not ready to get new data. The Busy condition, as defined in the MultiMediaCard Specification, may occur after or within the block transfer of any write or erase operations. After a host command is sent, the host shall expect to get a Busy indication in any case that response of type R1b is expected. The RDY/BSY\_B indication is basically the same as the Busy indication that is indicated by DAT0 (as given in the MultiMediaCard Specification).

# 3.4.5.2. Write Protect Function [Input + Pullup]

This line shall be set to "0" (or maximum 10KOhm pull down resistor) in order to eliminate any write operations to the TriFlash memory. An attempt to write to the TriFlash in that condition will set the WP\_VIOLATION status bit (bit [26] in the Card Status).

## 3.4.5.3. Reset Function [Input + Pullup]

If input is set to "0" (or maximum 10KOhm pull down resistor) it will force a Hardware RESET to the TriFlash.

# 3.5. TriFlash Registers

The device interface contains a set of four registers. The OCR, CID and CSD registers carry the device configuration information. The RCA register holds the device-relative communication address for the current session.

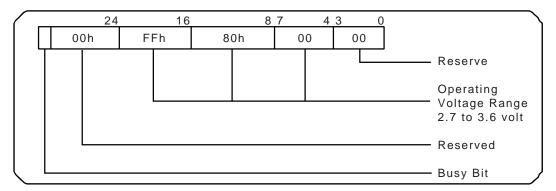

## 3.5.1. Operating Conditions Register (OCR)

The 32-bit OCR register stores the  $V_{DD}$  voltage profile of the device. The TriFlash is capable of executing the voltage recognition procedure (CMD1) with any standard TriFlash host using operating voltages from 2 to 3.6 Volts. Accessing the data in the memory array, however, requires 2.7 to 3.6 Volts. The OCR shows the voltage range in which the device data can be accessed. The structure of the OCR register is described in Table 3-8.

Table 3-8. OCR Register Definition

| OCR Bit | VDD Voltage Window                |

|---------|-----------------------------------|

| 0-7     | Reserved                          |

| 8       | 2.0-2.1                           |

| 9       | 2.1-2.2                           |

| 10      | 2.2-2.3                           |

| 11      | 2.3-2.4                           |

| 12      | 2.4-2.5                           |

| 13      | 2.5-2.6                           |

| 14      | 2.6-2.7                           |

| 15      | 2.7-2.8                           |

| 16      | 2.8-2.9                           |

| 17      | 2.9-3.0                           |

| 18      | 3.0-3.1                           |

| 19      | 3.1-3.2                           |

| 20      | 3.2-3.3                           |

| 21      | 3.3-3.4                           |

| 22      | 3.4-3.5                           |

| 23      | 3.5-3.6                           |

| 24-30   | Reserved                          |

| 31      | Device power up status bit (busy) |

The level coding of the OCR register is as follows:

- Restricted voltage windows=LOW

- Device busy=LOW (bit 31)

The least significant 31 bits are constant and will be set as described in Figure 3-6. If set, bit 32, the busy bit, informs the host that the device power up procedure is finished.

Figure 3-6. OCR Structure

#### 3.5.2. Card Identification (CID) Register

The CID register is 16 bytes long and contains a unique device identification number as shown in Table 3-9. It is programmed during device manufacturing and cannot be changed by TriFlash hosts.

| Name                          | Туре   | Width | CID—Slice | CID—Value                 | Comments                                                                                                                                            |

|-------------------------------|--------|-------|-----------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer ID (MID)         | Binary | 8     | [127:120] | 0x02                      | The manufacturer IDs are controlled and assigned by the MultiMediaCard Association.                                                                 |

| OEM/Application ID (OID)      | Binary | 16    | [119:104] | 0x0000                    | Identifies the device OEM and/or the device contents. The OID is assigned by the MMCA. This field may be specifically configured for OEM customers. |

| Product Name (PNM)            | String | 48    | [103:56]  | See footnote <sup>1</sup> | 6 ASCII characters long.                                                                                                                            |

| Product Revision (PRV)        | BCD    | 8     | [55:48]   | See footnote <sup>2</sup> | Two binary coded decimal digits.                                                                                                                    |

| Serial Number (PSN)           | Binary | 32    | [47:16]   |                           | 32 Bits unsigned integer.                                                                                                                           |

| Manufacturing Date Code (MDT) | BCD    | 8     | [15:8]    | See footnote <sup>3</sup> | Manufacturing date-mm/yy (offset from 1997).                                                                                                        |

| CRC7 checksum (CRC)           | Binary | 7     | [7:1]     | See footnote <sup>4</sup> | Calculated.                                                                                                                                         |

| Not used, always '1'          |        | 1     | [0:0]     |                           |                                                                                                                                                     |

Table 3-9. CID Fields

SDAT1FAH-128 STM016 SDBT1FAH-256 STM032 SDBT1FCH-512 STM064 SDBT1FCH-1024 STM128

CRC Calculation: G(x)=x7+3+1 M(x)=(MID-MSB)\*x119+...+(CIN-LSB)\*x0CRC[6...0]=Remainder[(M(x)\*x7)/G(x)]

<sup>&</sup>lt;sup>1</sup> Model Name Name in CD Field

The product revision is composed of two Binary Coded Decimal (BCD) digits, four bits each, representing an "n.m" revision number. The "n" is the most significant nibble and the "m" is the least significant nibble. Example: The PRV binary value filed for product revision "6.2" will be: 0110 0010.

As an example, this field value for a March 2001 manufacturing date will be: 0011 0100.

<sup>&</sup>lt;sup>4</sup> The CRC Checksum is computed by the following formula:

## 3.5.3. Card Specific Data (CSD) Register

The CSD register contains all the configuration information required in order to access the device data. In Table 3-10, the Cell Type column defines the CSD field as Read only (R), One Time Programmable (R/W) or erasable (R/W/E). This table shows, for each field, the value in "real world" units and coded according to the CSD structure. The Model Dependent column marks (with a check mark— $\sqrt{}$ ) the CSD fields that are model dependent.

Table 3-10. CSD Register

| Field                 | Width<br>[bits] | Cell<br>Type | CSD-slice              | CSD Value             | CSD Code     | Model<br>Dep. | Description                                        |

|-----------------------|-----------------|--------------|------------------------|-----------------------|--------------|---------------|----------------------------------------------------|

| CSD_STRUCTURE         | 2               | R            | [127:126]              | V1.1                  | 1            |               | CSD Structure                                      |

| SPEC_VERS             | 4               | R            | [125:122]              | V2.2                  | 2            |               | MultiMediaCard Specification<br>Version            |

| -                     | 2               | R            | [121:120]              | 0                     | 0            |               | Reserved                                           |

| TAAC<br>Binary<br>MLC | 8               | R<br>R       | [119:112]<br>[119:112] | 1.5msec<br>10msec     | 0x0F<br>0x0F |               | Data Read Access-Time-1<br>Data Read Access-Time-1 |

| NSAC                  | 8               | R            | [111:104]              | 0                     | 0            |               | Data Read Access-Time-2 in CLK Cycles (NSAC*100)   |

| TRAN_SPEED            | 8               | R            | [103:96]               | 20MHZ                 | 0x2A         |               | Max. Data Transfer Rate                            |

| CCC                   | 12              | R            | [95:84]                | See note <sup>1</sup> | 0x0F5        |               | Card Command Classes                               |

| READ_BL_LEN           | 4               | R            | [83:80]                | 512                   | 9            |               | Max. Read Data Block Length                        |

| READ_BL_PARTIAL       | 1               | R            | [79:79]                | Yes                   | 1            |               | Partial Blocks for Read Allowed                    |

| WRITE_BLK_MISALIGN    | 1               | R            | [78:78]                | No                    | 0            |               | Write Block Misalignment                           |

| READ_BLK_MISALIGN     | 1               | R            | [77:77]                | No                    | 0            |               | Read Block Misalignment                            |

| DSR_IMP               | 1               | R            | [76:76]                | No                    | 0            |               | DSR Implemented                                    |

| -                     | 2               | R            | [75:74]                | 0                     | 0            |               | Reserved                                           |

| C_SIZE                | 12              | R            | [73:62]                |                       |              | V             | Device Size (C_SIZE)                               |

| VDD_R_CURR_MIN        | 3               | R            | [61:59]                | 60mA                  | 6            |               | Max. Read Current @V <sub>DD</sub> Min.            |

| VDD_R_CURR_MAX        | 3               | R            | [58:56]                | 80mA                  | 6            |               | Max. Read Current @VDD Max.                        |

| VDD_W_CURR_MIN        | 3               | R            | [55:53]                | 60mA                  | 6            |               | Max. Write Current @VDD Min.                       |

| VDD_W_CURR_MAX        | 3               | R            | [52:50]                | 80mA                  | 6            |               | Max. Write Current @V <sub>DD</sub> Max.           |

| C_SIZE_MULT           | 3               | R            | [49:47]                |                       |              | √             | Device Size Multiplier (C_SIZE_MULT)               |

| SECTOR_SIZE           | 5               | R            | [46:42]                | 1                     | 0            |               | Erase Sector Size                                  |

| ERASE_GRP_SIZE        | 5               | R            | [41:37]                |                       |              | V             | Erase Group Size                                   |

| WP_GRP_SIZE           | 5               | R            | [36:32]                | 32                    | 0x1F         | _             | Write Protect Group Size                           |

| WP_GRP_ENABLE         | 1               | R            | [31:31]                | Yes                   | 1            |               | Write Protect Group Enable                         |

| DEFAULT_ECC           | 2               | R            | [30:29]                | None                  | 0            |               | Manufacturer Default ECC                           |

<sup>&</sup>lt;sup>1</sup> This SanDisk product does not support the following classes: I/O, application specific, stream write, and stream read.

| Field                | Width<br>[bits] | Cell<br>Type | CSD-slice | CSD Value | CSD Code | Model<br>Dep. | Description                                |

|----------------------|-----------------|--------------|-----------|-----------|----------|---------------|--------------------------------------------|

| R2W_FACTOR<br>Binary | 3               | R            | [28:26]   | 1:16      | 2        |               | Read to Write Speed Factor                 |

| MLC                  | 3               | R            | [28:26]   | 1:4       | 2        |               | Read to Write Speed Factor                 |

| WRITE_BL_LEN         | 4               | R            | [25:22]   | 512       | 9        |               | Max. Write Data Block Length               |

| WRITE_BL_PARTIAL     | 1               | R            | [21:21]   | No        | 0        |               | Partial Blocks for Write Allowed           |

| -                    | 5               | R            | [20:16]   | 0         | 0        |               | Reserved                                   |

| FILE_FORMAT_GRP      | 1               | R/W          | [15:15]   | 0         | 0        |               | Indicates File Format of<br>Selected Group |

| COPY                 | 1               | R/W          | [14:14]   | Сору      | 1        |               | Copy Flag (OTP)                            |

| PERM_WRITE_PROTECT   | 1               | R/W          | [13:13]   | No        | 0        |               | Permanent Write Protection                 |

| TMP_WRITE_PROTECT    | 1               | R/W/E        | [12:12]   | No        | 0        |               | Temporary Write Protection                 |

| FILE_FORMAT          | 2               | R/W          | [11:10]   | 0         | 0        |               | File Format of Card                        |

| ECC                  | 2               | R/W/E        | [9:8]     | None      | 0        |               | ECC Code                                   |

| CRC                  | 7               | R/W/E        | [7:1]     |           |          | <b>V</b>      | CRC                                        |

| -                    | 1               | -            | [0:0]     | 1         | 1        |               | Not Used, Always '1'                       |

The following sections describe the CSD fields and the relevant data types. If not explicitly defined otherwise, all bit strings are interpreted as binary coded numbers starting with the left bit first.

**CSD STRUCTURE**—describes the version of the CSD structure.

Table 3-11. CSD Register Structure

| CSD_STRUCTURE | CSD Structure Version | Valid for MultiMediaCard Protocol Version |  |

|---------------|-----------------------|-------------------------------------------|--|

| 0             | CSD version No. 1.0   | MultiMediaCard protocol version 1.0–1.2   |  |

| 1             | CSD version No. 1.1   | MultiMediaCard protocol version 1.4–2.2   |  |

| 2—3           | Reserved              | Reserved                                  |  |

**MMC\_PROT**—Defines the MultiMediaCard protocol version supported by the device. It includes the definition of the command set and the device responses. The card identification procedure is compatible for all protocol versions.

Table 3-12. MultiMediaCard Protocol Version

| SPEC_VERS | MultiMediaCard Protocol Version         |

|-----------|-----------------------------------------|

| 0         | MultiMediaCard protocol version 1.0–1.2 |

| 1         | MultiMediaCard protocol version 1.4     |

| 2         | MultiMediaCard protocol version 2.0–2.2 |

| 3-15      | Reserved                                |

TAAC—Defines the asynchronous part (relative to the MultiMediaCard bus clock (CLK)) of the read access time.

**Table 3-13. TAAC Access Time Definition**

| TAAC Bit<br>Position | Code                                                                                                                                    |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2:0                  | time exponent<br>0=1ns, 1=10ns, 2=100ns, 3=1µms, 4=10µms, 5=100µms,<br>6=1ms, 7=10ms                                                    |

| 6:3                  | time mantissa<br>0=Reserved, 1=1.0, 2=1.2, 3=1.3, 4=1.5, 5=2.0, 6=2.5, 7=3.0,<br>8=3.5, 9=4.0, A=4.5, B=5.0, C=5.5, D=6.0, E=7.0, F=8.0 |

| 7                    | Reserved                                                                                                                                |

**NSAC**—Defines the worst case for the clock dependent factor of the data access time. The unit for NSAC is 100 clock cycles. Therefore, the maximal value for the clock dependent part of the read access time is 25.5k clock cycles.

The total read access time  $N_{AC}$  as expressed in the Table 3-14 is the sum of TAAC and NSAC. It has to be computed by the host for the actual clock rate. The read access time should be interpreted as a typical delay for the first data bit of a data block or stream from the end bit on the read commands.

**TRAN\_SPEED**—Table 3-14 defines the maximum data transfer rate TRAN\_SPEED.

Table 3-14. Maximum Data Transfer Rate Definition

| TRAN_SPEED Bit | Code                                                                                                                                    |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 2:0            | transfer rate exponent 0=100kbit/s, 1=1Mbit/s, 2=10Mbit/s, 3=100Mbit/s, 4 7=Reserved                                                    |

| 6:3            | time mantissa<br>0=Reserved, 1=1.0, 2=1.2, 3=1.3, 4=1.5, 5=2.0, 6=2.5, 7=3.0,<br>8=3.5, 9=4.0, A=4.5, B=5.0, C=5.5, D=6.0, E=7.0, F=8.0 |

| 7              | Reserved                                                                                                                                |

CCC—The TriFlash command set is divided into subsets (command classes). The card command class register CCC defines which command classes are supported by this device. A value of '1' in a CCC bit means that the corresponding command class is supported. For an explanation of command classes, see Section 4.6.3.

**Table 3-15. Supported Card Command Classes**

| CCC Bit | Supported Card Command Class |  |

|---------|------------------------------|--|

| 0       | class 0                      |  |

| 1       | class 1                      |  |

|         |                              |  |

| 11      | class 11                     |  |

**READ\_BL\_LEN**—The data block length is computed as 2<sup>READ\_BL\_LEN</sup>. The block length might therefore be in the range 1, 2, 4...2048 bytes.

Table 3-16. Data Block Length

| READ_BL_LEN | Block Length                 |  |

|-------------|------------------------------|--|

| 0           | 2º = 1 Byte                  |  |

| 1           | 21 = 2 Bytes                 |  |

|             |                              |  |

| 11          | 2 <sup>11</sup> = 2048 Bytes |  |

| 12-15       | Reserved                     |  |

**READ BL PARTIAL**—Defines whether partial block sizes can be used in block read commands.

READ\_BL\_PARTIAL=0 means that only the READ\_BL\_LEN block size can be used for block-oriented data transfers.

READ\_BL\_PARTIAL=1 means that smaller blocks can be used as well. The minimum block size will be equal to minimum addressable unit (one byte).

**WRITE\_BLK\_MISALIGN**—Defines if the data block to be written by one command can be spread over more than one physical block of the memory device. The size of the memory block is defined in WRITE BL LEN.

WRITE BLK MISALIGN=0 signals that crossing physical block boundaries is invalid.

WRITE BLK MISALIGN=1 signals that crossing physical block boundaries is allowed.

**READ\_BLK\_MISALIGN**—Defines if the data block to be read by one command can be spread over more than one physical block of the memory device. The size of the memory block is defined in READ\_BL\_LEN.

READ BLK MISALIGN=0 signals that crossing physical block boundaries is invalid.

READ BLK MISALIGN=1 signals that crossing physical block boundaries is allowed.

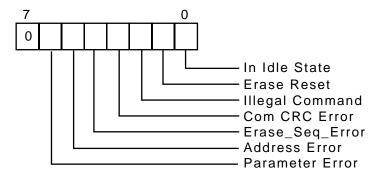

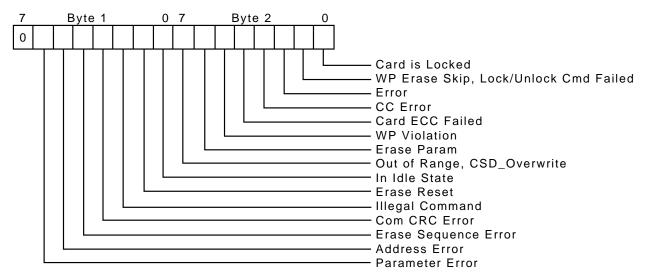

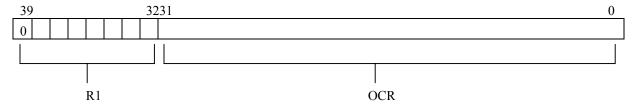

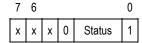

**DSR\_IMP**—Defines if the configurable driver stage is integrated on the device. If set, a driver stage register (DSR) must be implemented also.